Zeroplus LAP-F1 series

Détails

The logic analysers in the LAP-F1 series are multi-purpose PC based logic analysers with a high sample rate, many channels and a huge number of decoding packages.

Details

All LAP-F1 series analysers work on Windows 32 bit and Windows 64 bit versions. The analysis is performed in the device with a Xilinx high-performance FPGA and exclusive active probes which improves sampling precision and stability. The protocol library contains over 110 different protocols that can be decoded 'out of the box'. In addition, various options are available such as direct data streaming and eMMC decoding. The 'channel folding' option is included by default nowadays, which makes it possible to combine the memory of multiple inactive channels, in order to increase the memory depth. The connection to a computer is controlled by a USB 3.0 connection.

User interface

The interface of the LAP-F1 software corresponds to that of the LAP-C in the sense that the software allows easy debugging. All functionality can be accessed from the main menu, but commonly used options can also be placed in a 'quick acces' bar for easy use. The known trigger and channel settings can be found on the left side of the screen. Below is an image of the software.

Models

The models in the LAP-F1 series differ mainly in memory depth and channels. The memory depth depends on the number of channels used. The table below shows the differences.

| Model | Channels | Memory depth per channel | Price |

|---|---|---|---|

| LAP-F140512M | 40 | 512 Mbit (40 channels) 1 Gbit (16 channels) |

|

| LAP-F16464M | 64 | 64 Mbit (64 channels) 128 Mbit (32 channels) 256 Mbit (16 channels) 512 Mbit (8 channels) 1Gbit (4 channels) |

|

| LAP-F164256M | 64 | 256 Mbit (64 channels) 512 Mbit (32 channels) 1Gbit (16 channels) |

|

| LAP-F164512M | 64 | 512 Mbit (64 channels) 1Gbit (32 channels) |

Specifications

| Bandwidth | 200 MHz |

| Vertical resolution | 12 Bits, 2.44 mV/step |

| Input impedance | 190 to 500 kΩ (±10%) |

| Input capacitance | 4.3 to 8.2 pF (± 2pF) |

| Supported OS | Windows 8.1 and 7 32 and 64 bit |

| Connectivity | USB 3.0 (prefered), USB 2.0 (compatible) |

| Dimensions | 322 x 180 x 38 mm |

| Weight | 4.1 - 4.4 kg |

For more information, please consult the manual and datasheet below.

LAP-F1 series important software functionality

An important part of the software possibilities is shown in a table below.

| Add bars | Auto save | Auto run | Automatic updates |

| DSO connection | Files compression | File Export | General software description |

| Multiple languages | Memory view | Navigator | Packet list |

| Pre/post triggering | Protocol decoders (>110) | Protocol Triggers (HW) | Real-time signal activity |

| State list and waveform view | Statistics | Trace information | Trigger delay |

| Trigger events | Trigger in/out | Trigger Mark | Trigger pass counter |

| Trigger sequence level | Trigger Voltage | Waveform and UI customization | Zooming and panning |

More information about the different free protocol decoding packages can be found on the website of Zeroplus .

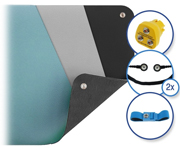

Accessories

The accessories supplied with the LAP-F1 series depend on the number of channels, an overview can be found below.

| Channels | 40 | 64 |

| CD with driver, software and manual | 1 | 1 |

| eMMC probes | 4 | 4 |

| eMMC Clock In probe | 1 | 1 |

| USB 3.0 cable (A-A type 32.5 cm) | 25 | 37 |

| Signal/earth cable pair | 40 | 64 |

| Clip-on connector | 80 | 128 |

| USB 3.0 cable PC-LAP F1 | 1 | 1 |

| BNC cable | 1 | 1 |

| Power cord | 1 | 1 |

Options

If you are interested in one of the options below, please contact us about the possibilities.

Software

| With special eMMC probes and 32 channels on 2 GHz, eMMC can be fully decoded and triggered. The long time record option is also included. | |

| With the long-term acquisition, the device can stream directly to a computer to perform, for example, burn in tests for a very long time. |

Accessories

Téléchargements

| LAP-F User Guide |

Download |